CPU/Adresseinheit und Busschnittstelle: Unterschied zwischen den Versionen

Erscheinungsbild

Die Seite wurde neu angelegt: „=Adresseinheit (AU) & Busschnittstelle (BIU)= * Der Aufbau der AU mit einem zentralen Addierer in Bild 5 ähnelt dem der ALU. * Tatsächlich wurde die Adressb…“ |

K Dirkwagner verschob die Seite CPU:Adresseinheit und Busschnittstelle nach CPU/Adresseinheit und Busschnittstelle, ohne dabei eine Weiterleitung anzulegen: Textersetzung - „:“ durch „/“ |

||

| (6 dazwischenliegende Versionen von 2 Benutzern werden nicht angezeigt) | |||

| Zeile 5: | Zeile 5: | ||

* Die spezialisierte AU erledigt das jedoch schneller und vor allem parallel zur ALU. | * Die spezialisierte AU erledigt das jedoch schneller und vor allem parallel zur ALU. | ||

* Der Decoder ist im einfachsten Fall als Linksschieberegister realisiert. | * Der Decoder ist im einfachsten Fall als Linksschieberegister realisiert. | ||

* Dieser Barrel Shifter extrahiert die Adressinformation aus dem Befehl durch Verschieben des Befehlscodes um n | * Dieser Barrel Shifter extrahiert die Adressinformation aus dem Befehl durch Verschieben des Befehlscodes um n Bit in nur einem Taktzyklus. | ||

* Die extrahierte Grundadresse gelangt dann in Hilfsregister A, wo Sie stabil anliegt bis der Addierer seine Arbeit beendet hat. | * Die extrahierte Grundadresse gelangt dann in Hilfsregister A, wo Sie stabil anliegt bis der Addierer seine Arbeit beendet hat. | ||

* Hilfsregister B beinhaltet den Inhalt des Programmzählers oder den des BIU-Adresspuffers. | * Hilfsregister B beinhaltet den Inhalt des Programmzählers oder den des BIU-Adresspuffers. | ||

| Zeile 25: | Zeile 25: | ||

* Die CPU arbeitet intern mit einer möglichst niedrigen Spannung, damit die Erwärmung bei hohen Taktfrequenzen in erträglichen Grenzen bleibt. | * Die CPU arbeitet intern mit einer möglichst niedrigen Spannung, damit die Erwärmung bei hohen Taktfrequenzen in erträglichen Grenzen bleibt. | ||

* Die BIU sorgt deshalb auch für eine Pegelanpassung zwischen dem CPU-Kern und dem externen Bussystem. | * Die BIU sorgt deshalb auch für eine Pegelanpassung zwischen dem CPU-Kern und dem externen Bussystem. | ||

[[Kategorie:CPU]] | |||

Aktuelle Version vom 29. März 2023, 12:34 Uhr

Adresseinheit (AU) & Busschnittstelle (BIU)

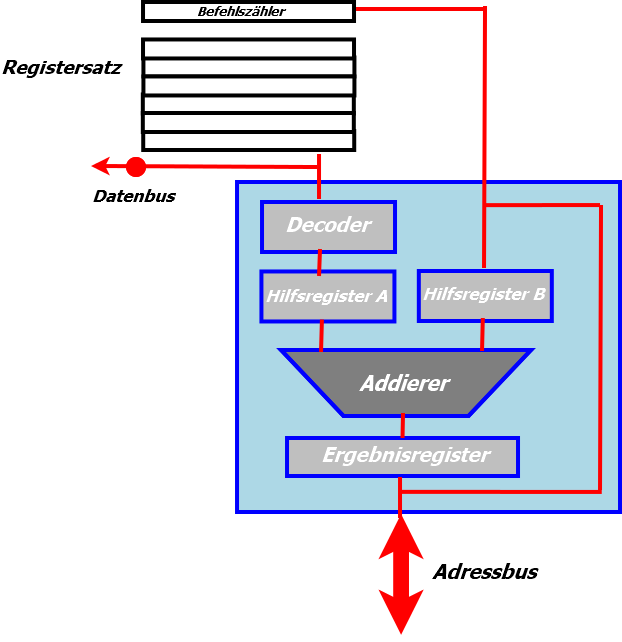

- Der Aufbau der AU mit einem zentralen Addierer in Bild 5 ähnelt dem der ALU.

- Tatsächlich wurde die Adressberechnung bei den ersten Prozessoren auch noch in dieser erledigt.

- Die spezialisierte AU erledigt das jedoch schneller und vor allem parallel zur ALU.

- Der Decoder ist im einfachsten Fall als Linksschieberegister realisiert.

- Dieser Barrel Shifter extrahiert die Adressinformation aus dem Befehl durch Verschieben des Befehlscodes um n Bit in nur einem Taktzyklus.

- Die extrahierte Grundadresse gelangt dann in Hilfsregister A, wo Sie stabil anliegt bis der Addierer seine Arbeit beendet hat.

- Hilfsregister B beinhaltet den Inhalt des Programmzählers oder den des BIU-Adresspuffers.

- Die komplexere MMU realer PC-Prozessoren kann darüber hinaus virtuelle Adressen verwalten.

- Das Betriebssystem lagert hierbei den Speicher blockweise auf die Festplatte aus.

- Greift die CPU auf den ausgelagerten Speicher zu, verursacht das einen Seitenfehler, der die MMU zum Handeln veranlasst.

- Das Betriebssystem blendet dann den gewünschten Speicherbereich in das RAM des PCs ein und lagert einen gerade nicht benötigten dafür aus.

- Den virtuellen Speicher kann die CPU dank MMU so ansprechen, als wäre er real existierendes RAM.

Address Unit: Die AU sorgt für die Berechnung der Adresse. In modernen CPUs verseht eine leistungsfähigere MMU diesen Dienst.

Busschnittstelle (BIU)

- Die Busschnittstelle verbindet die internen Busse des Prozessors mit der Außenwelt.

- Sie enthält Puffer zur Zwischenspeicherung von Adressen, Daten und Steuersignalen.

- Die CPU arbeitet intern mit einer möglichst niedrigen Spannung, damit die Erwärmung bei hohen Taktfrequenzen in erträglichen Grenzen bleibt.

- Die BIU sorgt deshalb auch für eine Pegelanpassung zwischen dem CPU-Kern und dem externen Bussystem.