Chipsatz: Unterschied zwischen den Versionen

Erscheinungsbild

K Textersetzung - „etc.“ durch „und weitere“ |

|||

| (23 dazwischenliegende Versionen von 6 Benutzern werden nicht angezeigt) | |||

| Zeile 9: | Zeile 9: | ||

** Anzahl der Speicherkanäle | ** Anzahl der Speicherkanäle | ||

** unterstützte Prozessoren | ** unterstützte Prozessoren | ||

** Verfügbare Schnittstellen (USB, SATA[[https://wiki. | ** Verfügbare Schnittstellen (USB, SATA[[https://wiki.foxtom.de/index.php?title=Hardware:SATA]], PCIe[[https://wiki.foxtom.de/index.php?title=PCI-Bus]] und weitere) | ||

** Anzahl der verfügbaren PCI-Express-Lanes | ** Anzahl der verfügbaren PCI-Express-Lanes | ||

** Anzahl der Schnittstellen | ** Anzahl der Schnittstellen | ||

** zusätzliche Integration von Geräten (Audio, WLAN | ** zusätzliche Integration von Geräten (Audio, WLAN und weitere) | ||

** Erweiterte Funktionen (RAID, Virtualisierung) | ** Erweiterte Funktionen (RAID, Virtualisierung) | ||

| Zeile 41: | Zeile 41: | ||

|- | |- | ||

| AMD X570 || Valhalla || Platform Controller Hub || AM4 || Q2 2019 | | AMD X570 || Valhalla || Platform Controller Hub || AM4 || Q2 2019 | ||

|} | |||

{| class="wikitable" | |||

|- | |||

! Chipsatz !! CPU-Unterstützung !! FSB !! RAM maximal !! PCI | |||

|- | |||

| NEAT || 286 || 4 bis 25 MHz || 8 MB || - | |||

|- | |||

| Intel 420TX || 486 || bis 33 MHz || 128 MB || PCI 1.0 | |||

|- | |||

| Intel 810 || Pentium II & III || 66 / 100 MHz || 512 MB || PCI 2.2 | |||

|- | |||

| Intel P55 || Core i3, i5, i7 || - || - || PCIe 2.0 | |||

|- | |||

| AMD X570 || Ryzen || - || - || PCIe 4.0 | |||

|} | |} | ||

| Zeile 49: | Zeile 64: | ||

* klassische Chipsatzarchitektur - bestehend aus North- & South-Bridge | * klassische Chipsatzarchitektur - bestehend aus North- & South-Bridge | ||

* Beide Chips sind Router - sie leiten den Datenverkehr von einem Bus zum anderen. | * Beide Chips sind Router - sie leiten den Datenverkehr von einem Bus zum anderen. | ||

[[Datei:NB-SB.svg|mini|links]] | |||

=== North-Bridge === | === North-Bridge === | ||

| Zeile 63: | Zeile 80: | ||

* als separater Chip in der Nähe der PCI-Steckplätze verbaut (im Süden der Platine) | * als separater Chip in der Nähe der PCI-Steckplätze verbaut (im Süden der Platine) | ||

* regelt den Datentransfer & die Datensteuerung zwischen den Geräten (SATA-Controller, USB, Netzwerk, Soundchip | * regelt den Datentransfer & die Datensteuerung zwischen den Geräten (SATA-Controller, USB, Netzwerk, Soundchip und weitere) | ||

* bezüglich der Leistungsfähigkeit geringere Anforderungen, als an die North-Bridge | * bezüglich der Leistungsfähigkeit geringere Anforderungen, als an die North-Bridge | ||

* Anbindung an die North-Bridge über PCI | * Anbindung an die North-Bridge über PCI | ||

=== Bus zwischen den Bridges === | === Bus zwischen den Bridges === | ||

* PCI: Ab den 1990er bis Anfang der 2000er Jahre wurden North- & South-Bridge über den PCI-Bus verbunden (33 MHz, 133 MB/s) | |||

* Hub Interface: proprietäre Schnittstelle, die von Intel 1998 mit dem ICH eingeführt wurde und die Datentransferrate gegenüber dem PCI-Bus verdoppelte (266 MB/s) | |||

* Direct Media Interface (DMI): | |||

** eine ebenfalls proprietäre Schnittstelle von Intel, die 2004 eingeführt wurde und das Hub-Interface ersetzte (1 GB/s) | |||

** DMI 2.0 folgte im Jahre 2011 und verdoppelte die Datentransferrate (2 GB/s) | |||

** DMI 3.0 wurde im Jahre 2015 eingeführt und verdoppelte die Geschwindigkeit abermals (3,93 GB/s) | |||

== Hub-Architektur == | == Hub-Architektur == | ||

[[Datei:MCH-ICH.png|mini|links]] | |||

* Einführung durch Intel (1999) - als Intel Hub Architecture (IHA) mit dem Intel 810 | * Einführung durch Intel (1999) - als Intel Hub Architecture (IHA) mit dem Intel 810 | ||

| Zeile 91: | Zeile 120: | ||

* Einführung im Jahre 2009 als Nachfolger der IHA | * Einführung im Jahre 2009 als Nachfolger der IHA | ||

* Durch Integration einiger Funktionen der North-Bridge in den Prozessor | * Durch Integration einiger Funktionen der North-Bridge in den Prozessor wird auf modernen Hauptplatinen nur noch ein Chip benötigt (I/O-Hub bzw. Platform-Controller-Hub (PCH)) | ||

* direkte Anbindung von Grafikkarte & Arbeitsspeicher an den Prozessor | * direkte Anbindung von Grafikkarte & Arbeitsspeicher an den Prozessor | ||

* Integration verbleibender North-Bridge-Funktionen & der gesamten Funktionalität der South-Bridge in den PCH | * Integration verbleibender North-Bridge-Funktionen & der gesamten Funktionalität der South-Bridge in den PCH | ||

* Kommunikation mit dem Prozessor über | * Kommunikation mit dem Prozessor über performante[[https://www.duden.de/rechtschreibung/performant]] Punkt-zu-Punkt-Verbindung (Direkt Media Interface (DMI) oder PCIe 4.0) | ||

=Links= | =Links= | ||

==Intern== | ==Intern== | ||

# https://wiki.foxtom.de/index.php?title=Hardware:SATA | |||

# https://wiki.foxtom.de/index.php?title=PCI-Bus | |||

==Extern== | ==Extern== | ||

TODO | |||

[[Kategorie:Mainboard]] | |||

Aktuelle Version vom 28. April 2025, 09:25 Uhr

Der Chipsatz ist eine Gruppe hochintegrierter Schaltkreise und die zentrale Komponente der Hauptplatine, über die sämtliche Datenströme zwischen Prozessor und Ein-/Ausgabegeräten laufen

Funktion

- Zentrales Bauelement auf dem Mainboard

- Bindeglied zwischen allen einzelnen Komponenten eines Computers

- Unterstützung des Prozessors bei der Steuerung der Kommunikation der Einzelkomponenten

- Bestimmt folgende Leistungsmerkmale:

Historie

Entwicklung

- vor 1987 eigenständige Schnittstellen-Chips, die über einen Adress-, Daten- und Steuerbus mit dem Prozessor verbunden & von diesem direkt angesprochen wurden

- 1987 erster Chipsatz für den 80286 (NEAT-Chipsatz - New Enhanced AT)

- 1990er Jahre Einführung einer Zwei-Brücken-Architektur

- 1998 Einführung der Intel-Hub-Architektur (IHA)

Wichtige Chipsätze

- Auflistung der ersten Chipsätze der jeweiligen Architektur und einem aktuellen Chipsatz.

| Chipsatz | Codename/Bezeichnung | Architektur | Sockel | Erscheinungsjahr |

|---|---|---|---|---|

| NEAT | "New Enhanced AT" | / | PGA68 | Q4 1987 |

| Intel 420TX | Saturn | Brücken-Architektur | Socket 2, Socket 3 | 1992 |

| Intel 810 | Whitney | Intel-Hub-Architektur | 370 | Q1 1999 |

| Intel P55 | Ibex Peak | Platform Controller Hub | 1156 | Q3 2009 |

| AMD X570 | Valhalla | Platform Controller Hub | AM4 | Q2 2019 |

| Chipsatz | CPU-Unterstützung | FSB | RAM maximal | PCI |

|---|---|---|---|---|

| NEAT | 286 | 4 bis 25 MHz | 8 MB | - |

| Intel 420TX | 486 | bis 33 MHz | 128 MB | PCI 1.0 |

| Intel 810 | Pentium II & III | 66 / 100 MHz | 512 MB | PCI 2.2 |

| Intel P55 | Core i3, i5, i7 | - | - | PCIe 2.0 |

| AMD X570 | Ryzen | - | - | PCIe 4.0 |

Aufbau

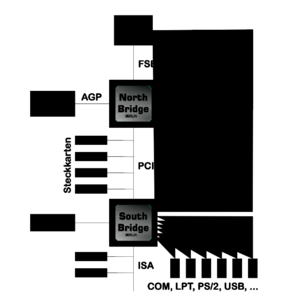

Bridge-Architektur

- klassische Chipsatzarchitektur - bestehend aus North- & South-Bridge

- Beide Chips sind Router - sie leiten den Datenverkehr von einem Bus zum anderen.

North-Bridge

- in unmittelbarer Nähe des Prozessors verbaut (im Norden der Platine)

- über den Front Side Bus direkt an den Prozessor angebunden

- breitbandig konzipiert & hoch getaktet (dadurch meist mit Kühlkörper versehen)

- Synchronisation des Datentransfers & der Datensteuerung zwischen Prozessor & Arbeitsspeicher

- stellt eine leistungsfähige Verbindung zur Grafikkarte her

- Grafikkarte & RAM mussten sich die verfügbare Bandbreite nicht mehr mit anderen Komponenten teilen

- enthielt bei älteren Mainboards auch den Speichercontroller

South-Bridge

- als separater Chip in der Nähe der PCI-Steckplätze verbaut (im Süden der Platine)

- regelt den Datentransfer & die Datensteuerung zwischen den Geräten (SATA-Controller, USB, Netzwerk, Soundchip und weitere)

- bezüglich der Leistungsfähigkeit geringere Anforderungen, als an die North-Bridge

- Anbindung an die North-Bridge über PCI

Bus zwischen den Bridges

- PCI: Ab den 1990er bis Anfang der 2000er Jahre wurden North- & South-Bridge über den PCI-Bus verbunden (33 MHz, 133 MB/s)

- Hub Interface: proprietäre Schnittstelle, die von Intel 1998 mit dem ICH eingeführt wurde und die Datentransferrate gegenüber dem PCI-Bus verdoppelte (266 MB/s)

- Direct Media Interface (DMI):

- eine ebenfalls proprietäre Schnittstelle von Intel, die 2004 eingeführt wurde und das Hub-Interface ersetzte (1 GB/s)

- DMI 2.0 folgte im Jahre 2011 und verdoppelte die Datentransferrate (2 GB/s)

- DMI 3.0 wurde im Jahre 2015 eingeführt und verdoppelte die Geschwindigkeit abermals (3,93 GB/s)

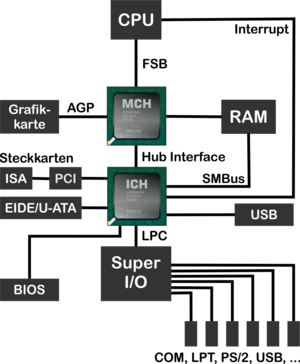

Hub-Architektur

- Einführung durch Intel (1999) - als Intel Hub Architecture (IHA) mit dem Intel 810

- Verbindung der beiden Controller über einen Hochgeschwindigkeitsbus, dem Hub-Interface (an Stelle des PCI-Busses)

- sternförmige Verbindung der einzelnen Komponenten (an Stelle der starren Nord-Süd-Achse)

- unterschiedliche Hubs erfüllen verschiedene Aufgaben

- Ausgliederung alter Verbindungen (Floppy, serielle & parallele Schnittstellen) in den Legacy-Port-Controller (LPC)

Memory-Controller-Hub (MCH)

- Funktionen entsprechen denen der North-Bridge

- kontrolliert den Datenfluß vom und zum Arbeitsspeicher

- Erhöhung der Bandbreite durch mehrere Kanäle für die Kommunikation mit dem Speicher

- auch als Graphics-Memory-Controller-Hub (GMCH) mit integriertem Grafikchip

I/O-Controller-Hub (ICH)

- übernimmt die Funktionen der South-Bridge

Platform Controller Hub

- Einführung im Jahre 2009 als Nachfolger der IHA

- Durch Integration einiger Funktionen der North-Bridge in den Prozessor wird auf modernen Hauptplatinen nur noch ein Chip benötigt (I/O-Hub bzw. Platform-Controller-Hub (PCH))

- direkte Anbindung von Grafikkarte & Arbeitsspeicher an den Prozessor

- Integration verbleibender North-Bridge-Funktionen & der gesamten Funktionalität der South-Bridge in den PCH

- Kommunikation mit dem Prozessor über performante[[3]] Punkt-zu-Punkt-Verbindung (Direkt Media Interface (DMI) oder PCIe 4.0)

Links

Intern

Extern

TODO