CPU: Unterschied zwischen den Versionen

| Zeile 145: | Zeile 145: | ||

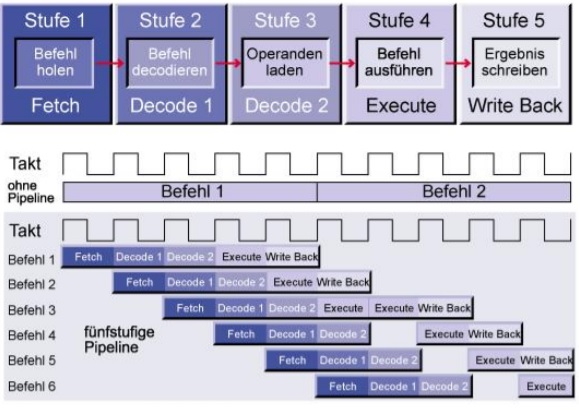

=Pipeline-Verfahren= | =Pipeline-Verfahren= | ||

[[Datei:008 Pipeline-Verfahren.jpg]] | |||

'''Pipeline in | |||

Pipeline in | |||

Funktion: Mit der | Funktion: Mit der | ||

Pipelining-Technik | Pipelining-Technik | ||

lässt sich die | lässt sich die | ||

Befehlsausführung | Befehlsausführung | ||

beschleunigen. | beschleunigen.''' | ||

=Superskalare Architektur= | =Superskalare Architektur= | ||

Version vom 7. Januar 2021, 13:07 Uhr

Central processing unit

Funktion

Mikroprozessoren sind hochkomplexe Maschinen. Sie basieren jedoch auf einem einfachen Grundprinzip. Wer es kennt, versteht auch die Funktionsweise der modernen CPUs.

History

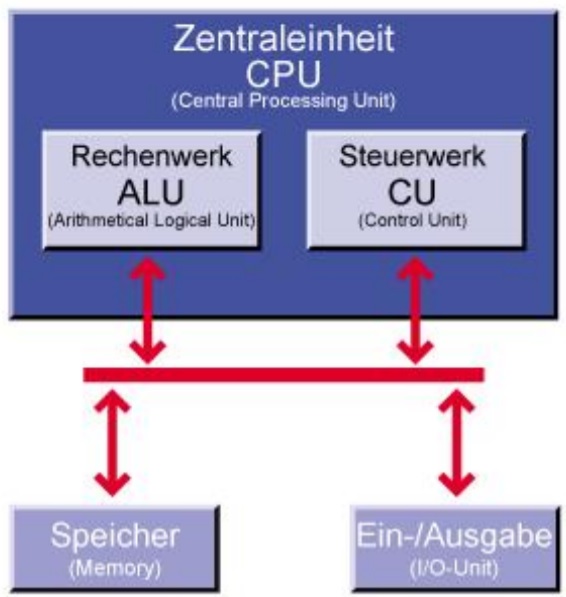

Von-Neumann-Rechner: Er beinhaltete schon vor 50 Jahren die wesentlichen Bestandteile heutiger PCs.

Von-Neumann-Rechner

Erweiterte Architektur

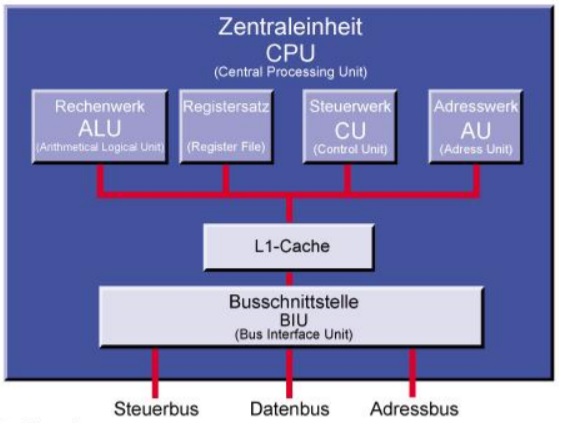

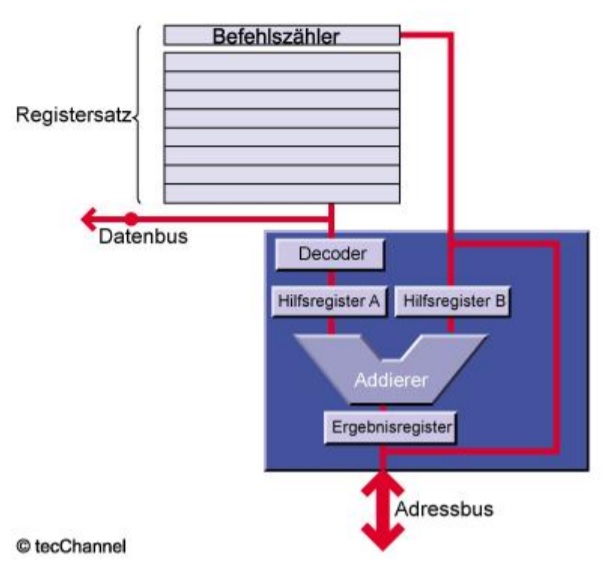

Beispiel-Prozessor: Die erweiterte tecChannel-CPU hat schon alles, was einen einfachen Mikroprozessor ausmacht.

Wie die einzelnen Funktionsblöcke genau arbeiten, klären wir in den folgenden

Abschnitten. Bevor wir aber ins Detail gehen, interessiert uns der grundsätzliche

Programmablauf im Prozessor:

- Holphase (Fetch): Zunächst muss ein Befehl aus dem Speicher (eventuell in

eines der Register) geladen werden. Wenn sich die gesuchte Information noch nicht im L1-Cache befindet, muss die BIU dafür den Speicher ansprechen.

- Dekodierphase (Decode): Das Steuerwerk untersucht den Befehl hinsichtlich der

vorzunehmenden Arbeitsschritte. Es entscheidet, welche Operation (Addition, Subtraktion, logische Verknüpfung und so weiter) die ALU auszuführen hat.

- Wenn für den Befehl noch Daten (Operanden) geholt werden müssen, steuert das

ebenfalls die CU. Dazu befehligt Sie auch das Adresswerk, das die Position der gewünschten Information ermittelt.

- Ausführungsphase (Execute): Die ALU wird vom Steuerwerk nun angewiesen,

die gewünschte Operation mit den geladenen Daten auszuführen

- Schreibphase (Write Back): Das Ergebnis der Operation landet (abhängig vom

Befehl) in einem der Register oder im Speicher. Um langwierige Zugriffe auf das externe RAM zu vermeiden, sammelt die CPU die Daten eventuell im L1-Cache, damit sie später in einem schnellen Blockschreibvorgang übertragen werden können.

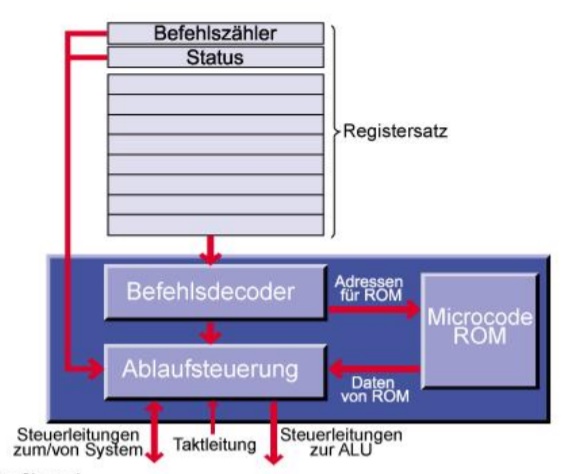

Steuereinheit (CU)

Die CU ist die Kommandozentrale der CPU. Sie steuert alle Abläufe im Innern des Prozessors sowie seine Kommunikation nach außen.

Control Unit: Die CU steuert alle Abläufe im Innern des Prozessors sowie seine Kommunikation nach außen.

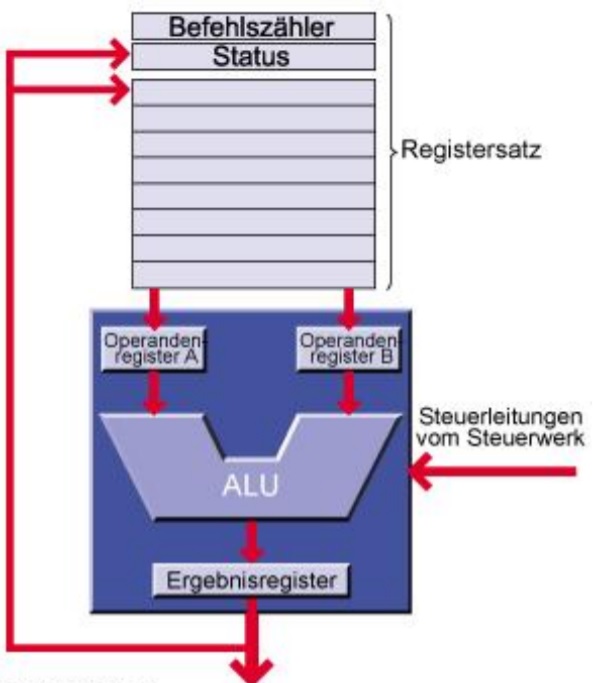

Rechenwerk (ALU)

Die ALU ist in der CPU für die Rechenarbeit zuständig. Alle aktuellen PC-Prozessoren besitzen neben einem oder mehreren dieser Rechenwerke für Ganzzahlen auch solche für Fließkommaarithmetik. Die FPUs ignorieren wir bei der Erläuterung der prinzipiellen Funktionsweise einer CPU, weil sie prinzipiell mit einer ALU gleichzusetzen ist.

Arithmetical and Logical Unit: Die ALU und ihr Datenweg. Die Hilfsregister für die Operanden und Ergebnisse gehören zu diesem Funktionsblock.

Adresseinheit (AU) & Busschnittstelle (BIU)

Address Unit: Die AU sorgt für die Berechnung der Adresse. In modernen CPUs verseht eine leistungsfähigere MMU diesen Dienst.

Busschnittstelle (BIU)

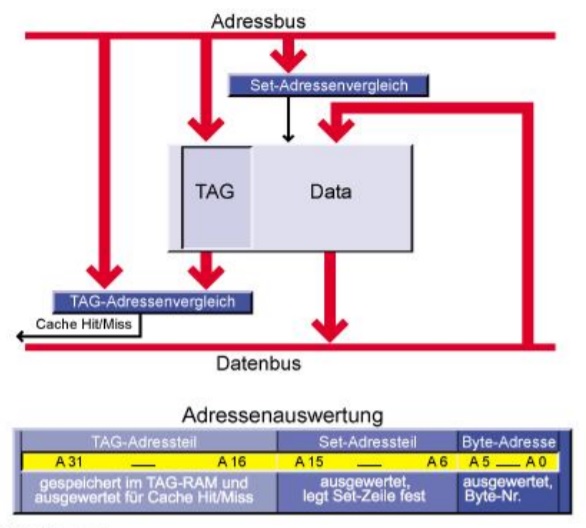

Cache-Grundlagen

Cache Interna: Der prinzipielle Aufbau eines Caches (oben) sowie die Adressauswertung im Cache-Controller (unten).

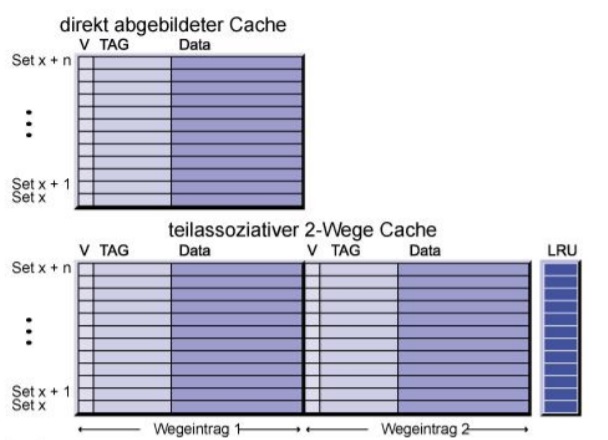

Cache-Organisation

Assoziativspeicher: Der teilassoziative Mehrweg-Cache beinhaltet im Prinzip mehrere Direct Mapped Caches plus Statistik-Bits (LRU).

Pipeline-Verfahren

Pipeline in Funktion: Mit der Pipelining-Technik lässt sich die Befehlsausführung beschleunigen.

Superskalare Architektur

Parallel ist schneller: Superskalare Architekturen mit einer doppelten Pipeline (oben) und parallel arbeitenden Ausführungseinheiten (unten).