CPU: Unterschied zwischen den Versionen

| Zeile 48: | Zeile 48: | ||

==Grundsätzliche Programmablauf im Prozessor | ==Grundsätzliche Programmablauf im Prozessor == | ||

Version vom 11. Februar 2021, 14:03 Uhr

Central processing unit

Funktion

Mikroprozessoren sind hochkomplexe Maschinen. Sie basieren jedoch auf einem einfachen Grundprinzip. Wer es kennt, versteht auch die Funktionsweise der modernen CPUs.

History

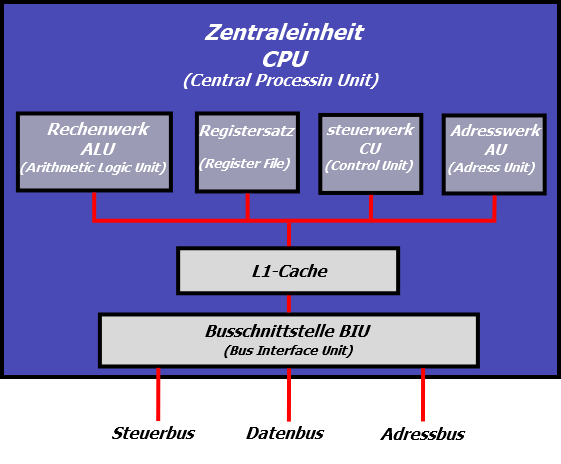

- Die Von-Neumann-Architektur besteht aus vier Funktionseinheiten, die in Bild 1 zu sehen sind: Rechenwerk, Steuerwerk, Speicher (Memory) und Ein-/Ausgabeeinheit (I/O-Unit).

- Dazu kommen noch die Verbindungen zwischen den Funktionsblöcken - das Bussystem.

- Die beiden wichtigsten Einheiten Rechenwerk und Steuerwerk sind im Prozessor vereint.

- Die CPU als Ganzes übernimmt innerhalb des Von-Neumann-Rechners die Ausführung von Befehlen und die notwendige Ablaufsteuerung.

Bild 1

Von-Neumann-Rechner: Er beinhaltete schon vor 50 Jahren die wesentlichen Bestandteile heutiger PCs.

Von-Neumann-Rechner

- Die Anpassung für jedes zu lösende Problem erfolgt mit im Speicher abgelegten Programmen.

- Diese Software beinhaltet die Informationen zur Steuerung des Rechners.

- Jede Speicherzelle ist mit einer festen Adresse eindeutig identifizierbar.

- In ihrer ursprünglichen Form verarbeitet sie mit nur einem Prozessor Schritt für Schritt Befehle und Daten, die aus dem Speicher stammen.

- Obwohl Befehle und Daten aus dem gleichen Speicher kommen, gibt es nur eine Busverbindung für Beides dorthin.

- So wurde eine hierarchisch gegliederte Speicherstruktur mit Registern und verschiedenen Cache-Ebenen eingeführt.

- Die sequenzielle Befehlsausführung wird in der CPU nach Kräften parallelisiert.

- Dazu stehen mehrere Funktionseinheiten und Ausführungsebenen bereit.

Erweiterte Architektur

- Der Von-Neumann-Rechner holt alle Befehle und Daten direkt aus dem Speicher. Für die heutigen CPUs wäre das viel zu langsam.

- Diese CPU orientiert sich hinsichtlich ihrer Arbeitsweise stark an den x86-Prozessor der PCs.

- Deshalb besitzt sie einen zusätzlichen Registersatz, der den Zugriff auf Befehle und Daten ohne Wartezyklen ermöglicht.

- Es handelt sich um Mehrzweckregister für Befehle und Daten.

- Das Adresswerk ist für die Berechnung der effektiven Adresse zuständig.

- Zusätzlich entkoppelt der L1-Cache den Prozessorkern vom langsamen externen Speicher.

Bild 2

Beispiel-Prozessor: Die erweiterte CPU hat schon alles, was einen einfachen Mikroprozessor ausmacht.

Grundsätzliche Programmablauf im Prozessor

Holphase (Fetch):

Zunächst muss ein Befehl aus dem Speicher geladen werden. Wenn sich die gesuchte Information noch nicht im L1-Cache befindet, muss die Busschnittstelle dafür den Speicher ansprechen.

Dekodierphase (Decode):

Das Steuerwerk untersucht den Befehl hinsichtlich der vorzunehmenden Arbeitsschritte. Es entscheidet, welche Operation (Addition, Subtraktion, logische Verknüpfung und so weiter) die ALU auszuführen hat.

Ausführungsphase (Execute):

Die ALU wird vom Steuerwerk nun angewiesen, die gewünschte Operation mit den geladenen Daten auszuführen

Schreibphase (Write Back):

Das Ergebnis der Operation landet in einem der Register oder im Speicher. Um langwierige Zugriffe auf das externe RAM zu vermeiden, sammelt die CPU die Daten eventuell im L1-Cache, damit sie später in einem schnellen Blockschreibvorgang übertragen werden können.

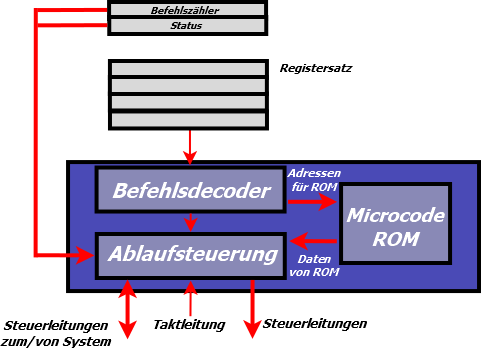

Steuereinheit (CU)

- Die CU ist die Kommandozentrale der CPU.

- Sie steuert alle Abläufe im Inneren des Prozessors sowie seine Kommunikation nach außen.

- Die CU holt sich einen Befehl aus dem Arbeitsspeicher/Cache und speichert ihn in einem Register zwischen.

- Damit ist der CPU-Bus frei für weitere Aktionen.

- Im Befehlsdecoder untersucht die CU die einzelnen Bits des Kommandos dann genauer.

- Aus einem Teil der Information ergibt sich der weitere logische und zeitliche Ablauf bei der Befehlsausführung.

- Handelt es sich um einen fest implementierten Befehl, werden sofort die entsprechenden Schritte in der Ablaufsteuerung eingeleitet.

- Sind alle zur Steuerung notwendigen Informationen gesammelt, beginnt die Ablaufsteuerung damit, das System zu koordinieren.

- Dazu gehört auch die Steuerung der BIU, um die Operanden für die Rechenbefehle in die Register zu laden.

Bild 3

Control Unit: Die CU steuert alle Abläufe im Innern des Prozessors sowie seine Kommunikation nach außen.

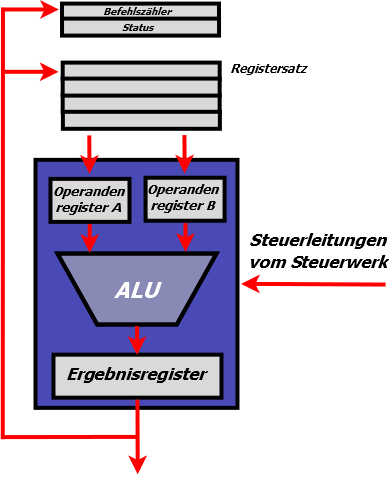

Rechenwerk (ALU)

- Die ALU ist in der CPU für die Rechenarbeit zuständig.

- Alle aktuellen PC-Prozessoren besitzen neben einem oder mehreren dieser Rechenwerke für Ganzzahlen auch solche für Fließkommaarithmetik.

- Das Bild zeigt den Datenweg unserer Beispiel-CPU.

- Die CU steuert die ALU, die auf Anweisung die beiden Operanden aus dem Registersatz holt, mit denen sie rechnen soll.

- Sie werden zunächst in den beiden Hilfsregistern zwischengepuffert, damit sie während der gesamten Rechenoperation stabil anliegen.

- Im nächsten Schritt führt die ALU die von der CU geforderte Rechenoperation aus.

- Das Resultat wird schließlich im Ergebnisregister zwischengepuffert, damit sich die ALU sofort der nächsten Aufgabe zuwenden kann.

Bild 4

Arithmetical and Logical Unit: Die ALU und ihr Datenweg. Die Hilfsregister für die Operanden und Ergebnisse gehören zu diesem nktionsblock.

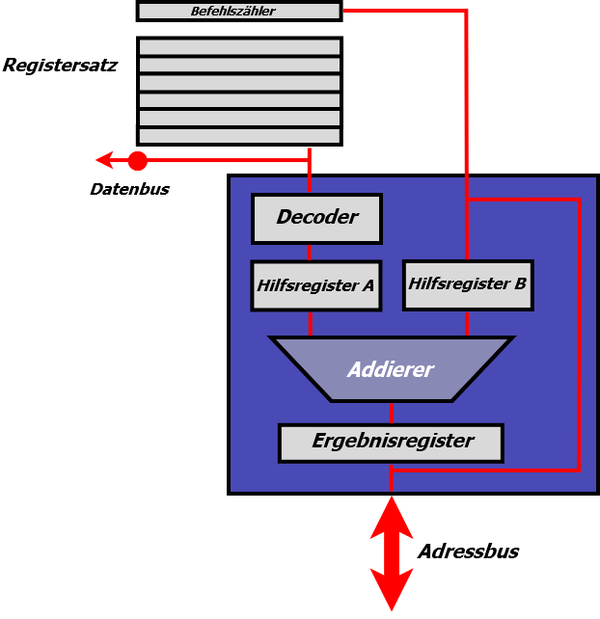

Adresseinheit (AU) & Busschnittstelle (BIU)

- Der Aufbau der AU mit einem zentralen Addierer in Bild 5 ähnelt dem der ALU.

- Tatsächlich wurde die Adressberechnung bei den ersten Prozessoren auch noch in dieser erledigt.

- Die spezialisierte AU erledigt das jedoch schneller und vor allem parallel zur ALU.

- Der Decoder ist im einfachsten Fall als Linksschieberegister realisiert.

- Dieser Barrel Shifter extrahiert die Adressinformation aus dem Befehl durch Verschieben des Befehlscodes um n Bits in nur einem Taktzyklus.

- Die extrahierte Grundadresse gelangt dann in Hilfsregister A, wo Sie stabil anliegt bis der Addierer seine Arbeit beendet hat.

- Hilfsregister B beinhaltet den Inhalt des Programmzählers oder den des BIU-Adresspuffers.

- Die komplexere MMU realer PC-Prozessoren kann darüber hinaus virtuelle Adressen verwalten.

- Das Betriebssystem lagert hierbei den Speicher blockweise auf die Festplatte aus.

- Greift die CPU auf den ausgelagerten Speicher zu, verursacht das einen Seitenfehler, der die MMU zum Handeln veranlasst.

- Das Betriebssystem blendet dann den gewünschten Speicherbereich in das RAM des PCs ein und lagert einen gerade nicht benötigten dafür aus.

- Den virtuellen Speicher kann die CPU dank MMU so ansprechen, als wäre er real existierendes RAM.

Bild 5

Address Unit: Die AU sorgt für die Berechnung der Adresse. In modernen CPUs verseht eine leistungsfähigere MMU diesen Dienst.

Busschnittstelle (BIU)

- Die Busschnittstelle verbindet die internen Busse des Prozessors mit der Außenwelt.

- Sie enthält Puffer zur Zwischenspeicherung von Adressen, Daten und Steuersignalen.

- Die CPU arbeitet intern mit einer möglichst niedrigen Spannung, damit die Erwärmung bei hohen Taktfrequenzen in erträglichen Grenzen bleibt.

- Die BIU sorgt deshalb auch für eine Pegelanpassung zwischen dem CPU-Kern und dem externen Bussystem.

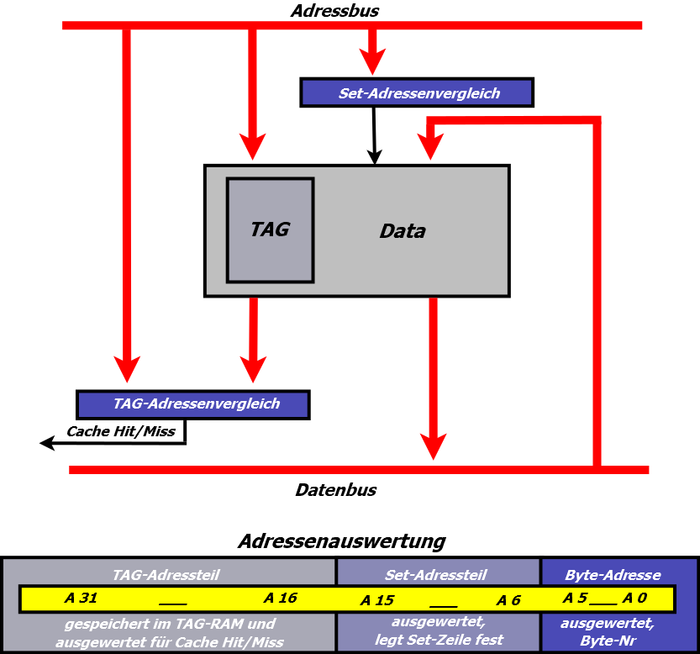

Cache-Grundlagen

- Zur Steigerung der Arbeitsleistung sitzt in der CPU zwischen den extrem schnellen Funktionseinheiten und dem vergleichsweise sehr langsamen Arbeitsspeicher der L1-Cache.

- Aus Platzgründen kann der L1-Cache in der CPU nicht besonders groß sein.

- Er bewegt sich in der Regel in Größenordnungen von 16 bis 64 KByte.

- Die Kunst besteht also darin, den schnellen kleinen Speicher so mit dem langsamen großen Arbeitsspeicher zu kombinieren, dass sich eine möglichst schnelle Gesamtlösung ergibt.

- Bild 6 zeigt die Auswertung einer 32-Bit-Adresse nach diesem Prinzip.

Bild 6

Cache Interna: Der prinzipielle Aufbau eines Caches (oben) sowie die Adressauswertung im Cache-Controller (unten).

Briefträger bei der Arbeit:

- Er trägt in einer Stadt (Arbeitsspeicher) die Post (Daten) aus.

- Dafür sortiert er die Post in seiner Tasche nach Straßen (Tag).

- In einer Straße holt er sich die hierfür bestimmte Post heraus und verteilt sie an die Häuser (Set-Zeile).

- Um in Mehrfamilienhäusern auch den richtigen Briefkasten zu erwischen, benötigt er noch den Familiennamen (Byte-Nummer).

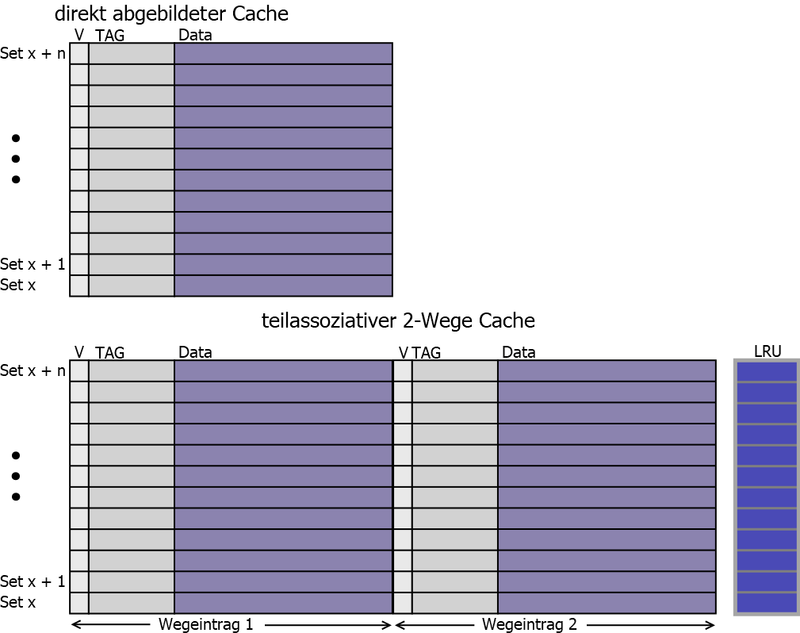

Cache-Organisation

- Der direkt abgebildete (direct mapped) Cache im Bild unten ist die einfachste Form.

- Jedem Set ist nur ein Cache-Eintrag zugeordnet.

- Dadurch deckt man im Arbeitsspeicher einen Block von x+n Sets ab.

Bild 7

Assoziativspeicher: Der teilassoziative Mehrweg-Cache beinhaltet im Prinzip mehrere Direct Mapped Caches plus Statistik-Bits (LRU).

Der Briefträger hat dieses Problem ebenfalls:

- Wenn er einen Abstecher in eine Seitenstraße macht, muss er den nach Straßen vorsortierten Briefstapel zurücklegen und den für die Seitenstraße herausholen.

- Die Lösung des Problems sind teilassoziative Mehrweg-Caches.

- Auch dieser Cache-Typ speichert nur einen Teil der Adresse im Tag ab.

- Taucht ein Tag aber nochmals auf, erfolgt kein Komplettaustausch des Speicherblocks.

- Die Hardware merkt sich den Eintrag wieder in der gleichen Set-Zeile.

- Allerdings erfolgt die Speicherung in einer weiteren Ebene (Weg), sodass die erste Zeile nicht überschrieben werden muss.

- Die Ebenenoder Wegauswahl erfolgt über den Set-Adressteil.

Mit einer Mehrwegsortierung arbeitet auch der Briefträger schneller:

- Er hat sich die Post nicht nur in Straßenzüge (Tag) unterteilt, sondern nochmals mit einem Gummiband hinsichtlich der Straßenseite gebündelt (Set-Weg).

- Bei einem Abstecher in die Seitenstrasse greift er sich nur das Briefbündel für eine Straßenseite.

- Dafür legt er nur eines der zwei Bündel der alten Straße weg - und zwar das von der anderen Straßenseite.

- Wenn er aus der Seitenstrasse zurückkommt, hat er immer noch das Bündel der Seite in der Hand, bei der er abgebogen ist.

- Ein Mehrweg-Cache ist ein vervielfachter Direct Mapped Cache.

- Der Schaltungsaufwand für einen teilassoziativen 2-Wege-Cache ist demnach doppelt so hoch wie bei der einfachen Version.

- Bei einem 4-Wege-Cache vervierfacht er sich.

- Irgendwann sind jedoch auch die Ebenen eines Mehrweg-Caches voll.

- Mittels zusätzlich gespeicherter LRU-Bits kann der Cache dann feststellen, welcher Eintrag in welcher Ebene am längsten nicht mehr benutzt wurde.

- Dieser Wegeintrag wird dann überschrieben.

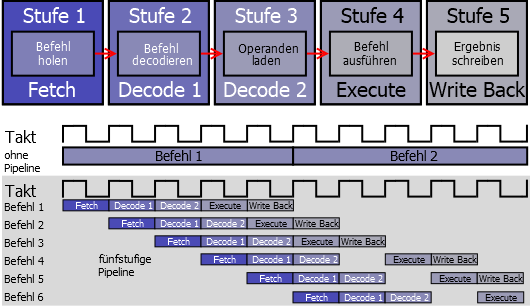

Pipeline-Verfahren

- Bis jetzt sind wir davon ausgegangen, dass die CPU die Befehle nach dem klassischen Von-Neumann-Prinzip nacheinander verarbeitet.

- Jeder Befehl wird innerhalb einer bestimmten Zeit (Taktzyklus) erledigt, dann ist der Nächste dran.

- Wenn man der BIU erlaubt, schon Befehle aus dem Speicher zu holen während die CU gerade einen analysiert, hat man zwei Arbeitsschritte parallelisiert.

- Es sind also zwei Befehle gleichzeitig in Teilbearbeitung. Überträgt man das Prinzip auf alle beteiligten Funktionseinheiten, erhöht sich die Zahl der Teilbearbeitungen weiter.

- Dieses Pipeline-Prinzip verarbeitet aber die eingehenden Befehle und Daten immer noch Schritt für Schritt.

Bild 8

Pipeline in Funktion: Mit der Pipelining-Technik lässt sich die Befehlsausführung beschleunigen.

Superskalare Architektur

- Wenn schon eine Pipeline die Geschwindigkeit erhöht, geht es mit Zweien noch schneller.

- In Bild 9 "Parallel ist schneller" ist im oberen Teil ein solcher Ansatz zu sehen.

- Auf diese Weise arbeitet beispielsweise der Intel Pentium.

- Um unnötige Probleme mit Abhängigkeiten zwischen den Befehlen zu minimieren, arbeitet die Intel-CPU allerdings nur bei Kommandos gleichzeitig mit beiden Pipelines, die gut zueinander passen.

Bild 9

Parallel ist schneller: Superskalare Architekturen mit einer doppelten Pipeline oben und parallel arbeitenden Ausführungseinheiten unten.

Sprungvorhersage

- Die Abhängigkeiten der Befehle untereinander sowie Sprungbefehle machen den Pipelines und superskalaren Architekturen zu schaffen.

- Je mehr parallel vorweggreifend erledigt wird, desto mehr Arbeit ist beispielsweise bei einem Sprungbefehl in ein anderes Programmsegment nachzuholen.

- Die ALUs müssen dann warten, bis sich die neuen Befehle durch die lange Pipeline gequält haben.

Dynamische Sprungvorhersage

Die Sprungvorhersage kann auf einfachen Regeln basieren:

- Beispielsweise ist es bei einem Sprungbefehl gegen den Befehlsstrom sehr wahrscheinlich, dass er mehrheitlich tatsächlich ausgeführt wird.

- Diese Annahme basiert auf der Feststellung, dass Rückwärtssprünge im Programmcode oft am Ende von Schleifen stehen.

- Und Programmschleifen werden in der Regel mehr als nur einmal durchlaufen.

- Bei Vorwärtssprüngen ist eine derart einfache Vorhersage kaum noch zu treffen.

- Hier kann man nur von der statistischen Erkenntnis ausgehen, dass die meisten bedingten Vorwärtssprünge nicht ausgeführt werden.