CPU/Erweiterte Von Neumann Architektur: Unterschied zwischen den Versionen

Erscheinungsbild

K Dirkwagner verschob die Seite Hardware:CPU:VonNeumannErweiterteArchitektur nach CPU:Erweiterte Von Neumann Architektur, ohne dabei eine Weiterleitung anzulegen |

K Textersetzung - „:Hardware:“ durch „:“ |

||

| Zeile 49: | Zeile 49: | ||

# Schreibphase (Write Back): Das Ergebnis der Operation landet in einem der Register oder im Speicher. Um langwierige Zugriffe auf das externe RAM zu vermeiden, sammelt die CPU die Daten eventuell im L1-Cache, damit sie später in einem schnellen Blockschreibvorgang übertragen werden können. | # Schreibphase (Write Back): Das Ergebnis der Operation landet in einem der Register oder im Speicher. Um langwierige Zugriffe auf das externe RAM zu vermeiden, sammelt die CPU die Daten eventuell im L1-Cache, damit sie später in einem schnellen Blockschreibvorgang übertragen werden können. | ||

[[Category | [[Category:CPU]] | ||

Version vom 20. Mai 2022, 10:18 Uhr

Central processing unit

Funktion

Mikroprozessoren sind hochkomplexe Maschinen. Sie basieren jedoch auf einem einfachen Grundprinzip. Wer es kennt, versteht auch die Funktionsweise der modernen CPUs.

History

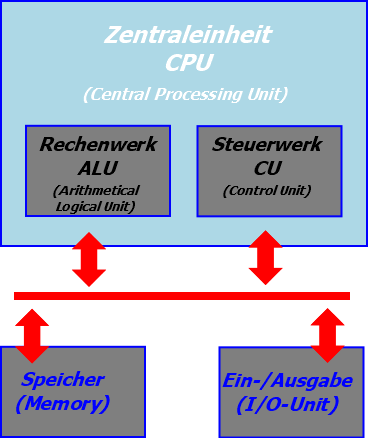

- Die Von-Neumann-Architektur besteht aus vier Funktionseinheiten, die in Bild 1 zu sehen sind: Rechenwerk, Steuerwerk, Speicher (Memory) und Ein-/Ausgabeeinheit (I/O-Unit).

- Dazu kommen noch die Verbindungen zwischen den Funktionsblöcken - das Bussystem.

- Die beiden wichtigsten Einheiten ALU und CU sind heute im Prozessor vereint.

- Die CPU als Ganzes übernimmt innerhalb des Von-Neumann-Rechners die Ausführung der Befehle und die hierfür notwendige laufsteuerung.

Von-Neumann-Rechner:Er beinhaltete schon vor 50 Jahren die wesentlichen Bestandteile heutiger PCs.

Von-Neumann-Rechner

- Die Anpassung für jedes zu lösende Problem erfolgt mit im Speicher abgelegten Programmen.

- Diese Software beinhaltet die Informationen zur Steuerung des Rechners.

- Jede Speicherzelle ist mit einer festen Adresse eindeutig identifizierbar.

- In ihrer ursprünglichen Form verarbeitet sie mit nur einem Prozessor Schritt für Schritt Befehle und Daten, die aus dem Speicher stammen.

- Obwohl Befehle und Daten aus dem gleichen Speicher kommen, gibt es nur eine Busverbindung für Beides dorthin.

- So wurde eine hierarchisch gegliederte Speicherstruktur mit Registern und verschiedenen Cache-Ebenen eingeführt.

- Die sequenzielle Befehlsausführung wird in der CPU nach Kräften parallelisiert.

- Dazu stehen mehrere Funktionseinheiten und Ausführungsebenen bereit.

Erweiterte Architektur

- Der Von-Neumann-Rechner holt alle Befehle und Daten direkt aus dem Speicher. Für die heutigen CPUs wäre das viel zu langsam.

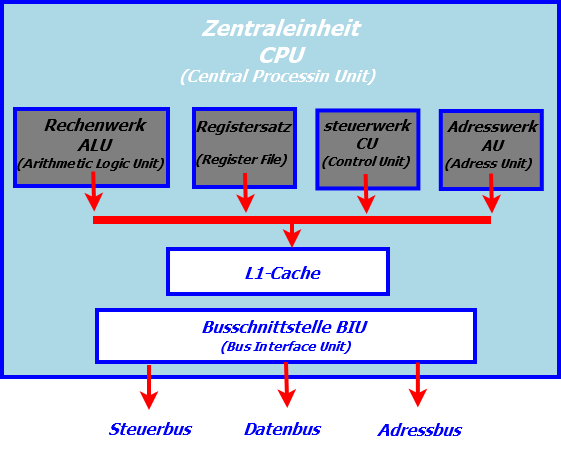

- Dieser CPU orientiert sich hinsichtlich Arbeitsweise stark an den x86-Prozessoren der PCs.

- Deshalb besitzt sie einen zusätzlichen Registersatz, der den Zugriff auf Befehle und Daten ohne Wartezyklen ermöglicht.

- Es handelt sich um Mehrzweckregister für Befehle und Daten.

- Das Adresswerk ist für die Berechnung der effektiven Adresse zuständig.

- Und der L1-Cache entkoppelt den Prozessorkern zusätzlich vom langsamen externen Speicher.

Beispiel-Prozessor: Die erweiterte CPU hat schon alles, was einen einfachen Mikroprozessor ausmacht.

Wie die einzelnen Funktionsblöcke genau arbeiten, klären wir in den folgenden Abschnitten. Bevor wir aber ins Detail gehen, interessiert uns der grundsätzliche Programmablauf im Prozessor:

- Holphase (Fetch): Zunächst muss ein Befehl aus dem Speicher geladen werden. Wenn sich die gesuchte Information noch nicht im L1-Cache befindet, muss die BIU dafür den Speicher ansprechen.

- Dekodierphase (Decode): Das Steuerwerk untersucht den Befehl hinsichtlich der vorzunehmenden Arbeitsschritte. Es entscheidet, welche Operation (Addition, Subtraktion, logische Verknüpfung und so weiter) die ALU auszuführen hat. (Wenn für den Befehl noch Daten (Operanden) geholt werden müssen, steuert das ebenfalls die CU. Dazu befehligt Sie auch das Adresswerk, das die Position der gewünschten Information ermittelt.)

- Ausführungsphase (Execute): Die ALU wird vom Steuerwerk nun angewiesen, die gewünschte Operation mit den geladenen Daten auszuführen

- Schreibphase (Write Back): Das Ergebnis der Operation landet in einem der Register oder im Speicher. Um langwierige Zugriffe auf das externe RAM zu vermeiden, sammelt die CPU die Daten eventuell im L1-Cache, damit sie später in einem schnellen Blockschreibvorgang übertragen werden können.