CPU

Central processing unit

Funktion

Mikroprozessoren sind hochkomplexe Maschinen. Sie basieren jedoch auf einem einfachen Grundprinzip. Wer es kennt, versteht auch die Funktionsweise der modernen CPUs.

History

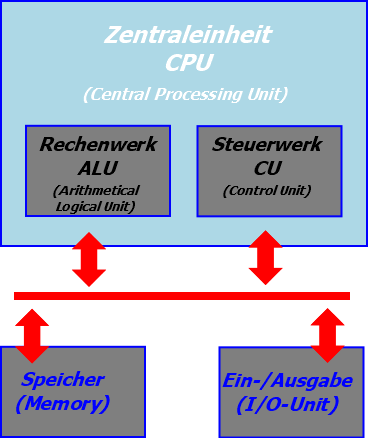

- Die Von-Neumann-Architektur besteht aus vier Funktionseinheiten, die in Bild 1 zu sehen sind: Rechenwerk, Steuerwerk, Speicher (Memory) und Ein-/Ausgabeeinheit (I/O-Unit).

- Dazu kommen noch die Verbindungen zwischen den Funktionsblöcken - das Bussystem.

- Die beiden wichtigsten Einheiten ALU und CU sind heute im Prozessor vereint.

- Die CPU als Ganzes übernimmt innerhalb des Von-Neumann-Rechners die Ausführung der Befehle und die hierfür notwendige laufsteuerung.

Von-Neumann-Rechner:Er beinhaltete schon vor 50 Jahren die wesentlichen Bestandteile heutiger PCs.

Von-Neumann-Rechner

- Die Anpassung für jedes zu lösende Problem erfolgt mit im Speicher abgelegten Programmen.

- Diese Software beinhaltet die Informationen zur Steuerung des Rechners.

- Jede Speicherzelle ist mit einer festen Adresse eindeutig identifizierbar.

- In ihrer ursprünglichen Form verarbeitet sie mit nur einem Prozessor Schritt für Schritt Befehle und Daten, die aus dem Speicher stammen.

- Obwohl Befehle und Daten aus dem gleichen Speicher kommen, gibt es nur eine Busverbindung für Beides dorthin.

- So wurde eine hierarchisch gegliederte Speicherstruktur mit Registern und verschiedenen Cache-Ebenen eingeführt.

- Die sequenzielle Befehlsausführung wird in der CPU nach Kräften parallelisiert.

- Dazu stehen mehrere Funktionseinheiten und Ausführungsebenen bereit.

Erweiterte Architektur

- Der Von-Neumann-Rechner holt alle Befehle und Daten direkt aus dem Speicher. Für die heutigen CPUs wäre das viel zu langsam.

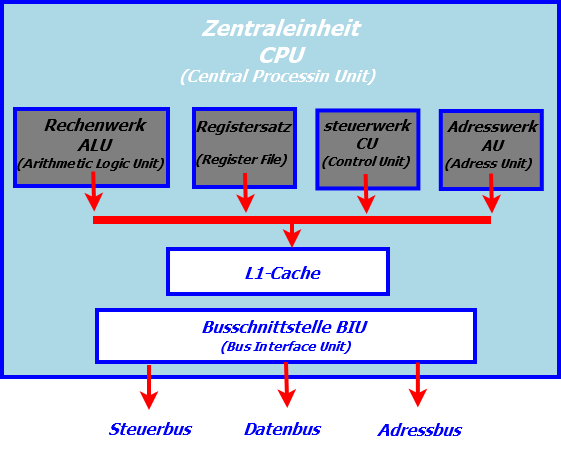

- Dieser CPU orientiert sich hinsichtlich Arbeitsweise stark an den x86-Prozessoren der PCs.

- Deshalb besitzt sie einen zusätzlichen Registersatz, der den Zugriff auf Befehle und Daten ohne Wartezyklen ermöglicht.

- Es handelt sich um Mehrzweckregister für Befehle und Daten.

- Das Adresswerk ist für die Berechnung der effektiven Adresse zuständig.

- Und der L1-Cache entkoppelt den Prozessorkern zusätzlich vom langsamen externen Speicher.

Beispiel-Prozessor: Die erweiterte CPU hat schon alles, was einen einfachen Mikroprozessor ausmacht.

Wie die einzelnen Funktionsblöcke genau arbeiten, klären wir in den folgenden Abschnitten. Bevor wir aber ins Detail gehen, interessiert uns der grundsätzliche Programmablauf im Prozessor:

- Holphase (Fetch): Zunächst muss ein Befehl aus dem Speicher geladen werden. Wenn sich die gesuchte Information noch nicht im L1-Cache befindet, muss die BIU dafür den Speicher ansprechen.

- Dekodierphase (Decode): Das Steuerwerk untersucht den Befehl hinsichtlich der vorzunehmenden Arbeitsschritte. Es entscheidet, welche Operation (Addition, Subtraktion, logische Verknüpfung und so weiter) die ALU auszuführen hat. (Wenn für den Befehl noch Daten (Operanden) geholt werden müssen, steuert das ebenfalls die CU. Dazu befehligt Sie auch das Adresswerk, das die Position der gewünschten Information ermittelt.)

- Ausführungsphase (Execute): Die ALU wird vom Steuerwerk nun angewiesen, die gewünschte Operation mit den geladenen Daten auszuführen

- Schreibphase (Write Back): Das Ergebnis der Operation landet in einem der Register oder im Speicher. Um langwierige Zugriffe auf das externe RAM zu vermeiden, sammelt die CPU die Daten eventuell im L1-Cache, damit sie später in einem schnellen Blockschreibvorgang übertragen werden können.

Steuereinheit (CU)

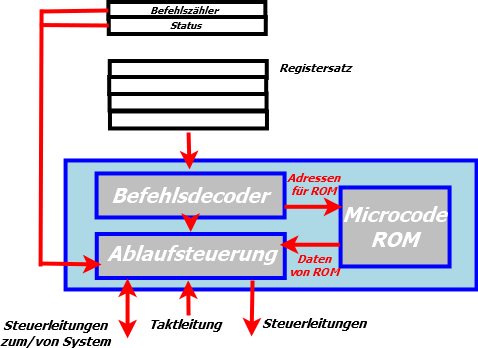

- Die CU ist die Kommandozentrale der CPU.

- Sie steuert alle Abläufe im Innern des Prozessors sowie seine Kommunikation nach außen.

- Die CU holt sich diesen Befehl aus dem Arbeitsspeicher/Cache und speichert ihn in einem Register zwischen.

- Damit ist der CPU-Bus frei für weitere Aktionen.

- Im Befehlsdecoder untersucht die CU die einzelnen Bits des commandos dann genauer.

- Aus einem Teil der Information ergibt sich der weitere logische und zeitliche Ablauf bei der Befehlsausführung.

- Handelt es sich um einen fest implementierten Befehl, werden sofort die entsprechenden Schritte in der Ablaufsteuerung eingeleitet.

- Sind alle zur Steuerung notwendigen Informationen gesammelt, beginnt die Ablaufsteuerung damit, das System zu koordinieren.

- Dazu gehört auch die Steuerung der BIU, um die Operanden für die Rechenbefehle in die Register zu laden.

Control Unit: Die CU steuert alle Abläufe im Innern des Prozessors sowie seine Kommunikation nach außen.

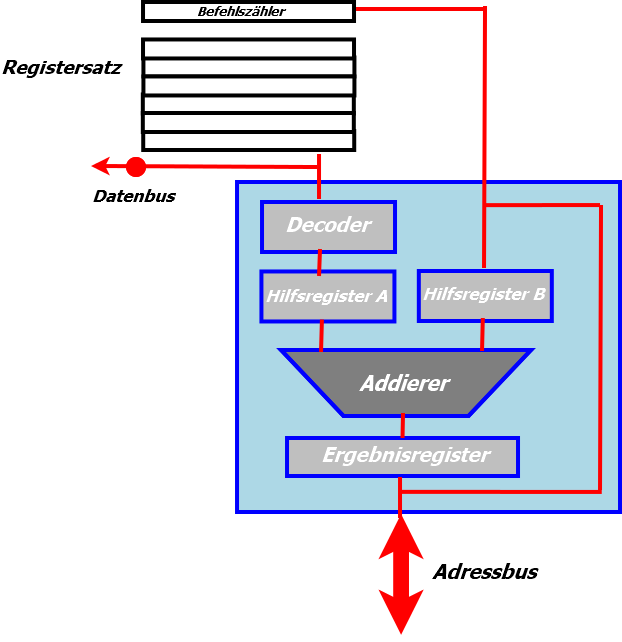

Rechenwerk (ALU)

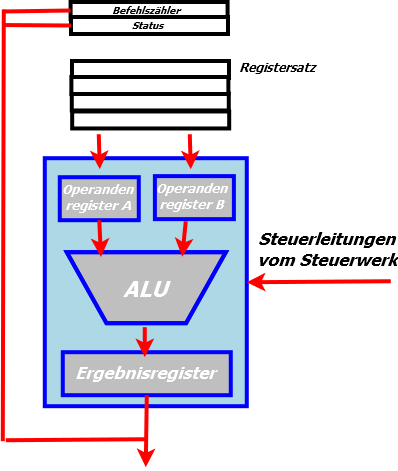

- Die ALU ist in der CPU für die Rechenarbeit zuständig.

- Alle aktuellen PC-Prozessoren besitzen neben einem oder mehreren dieser Rechenwerke für Ganzzahlen auch solche für Fließkommaarithmetik.

- Das Bild zeigt den Datenweg unserer Beispiel-CPU.

- Die CU steuert die ALU, die auf Anweisung die beiden Operanden aus dem Registersatz holt, mit denen sie rechnen soll.

- Sie werden zunächst in den beiden Hilfsregistern zwischengepuffert, damit sie während der gesamten Rechenoperation stabil anliegen.

- Im nächsten Schritt führt die ALU die von der CU geforderte Rechenoperation aus.

- Das Resultat wird schließlich im Ergebnisregister zwischengepuffert, damit sich die ALU sofort der nächsten Aufgabe zuwenden kann.

Arithmetical and Logical Unit: Die ALU und ihr Datenweg. Die Hilfsregister für die Operanden und Ergebnisse gehören zu diesem nktionsblock.

Adresseinheit (AU) & Busschnittstelle (BIU)

- Der Aufbau der AU mit einem zentralen Addierer in Bild 5 ähnelt dem der ALU.

- Tatsächlich wurde die Adressberechnung bei den ersten Prozessoren auch noch in dieser erledigt.

- Die spezialisierte AU erledigt das jedoch schneller und vor allem parallel zur ALU.

- Der Decoder ist im einfachsten Fall als Linksschieberegister realisiert.

- Dieser Barrel Shifter extrahiert die Adressinformation aus dem Befehl durch Verschieben des Befehlscodes um n Bits in nur einem Taktzyklus.

- Die extrahierte Grundadresse gelangt dann in Hilfsregister A, wo Sie stabil anliegt bis der Addierer seine Arbeit beendet hat.

- Hilfsregister B beinhaltet den Inhalt des Programmzählers oder den des BIU-Adresspuffers.

- Die komplexere MMU realer PC-Prozessoren kann darüber hinaus virtuelle Adressen verwalten.

- Das Betriebssystem lagert hierbei den Speicher blockweise auf die Festplatte aus.

- Greift die CPU auf den ausgelagerten Speicher zu, verursacht das einen Seitenfehler, der die MMU zum Handeln veranlasst.

- Das Betriebssystem blendet dann den gewünschten Speicherbereich in das RAM des PCs ein und lagert einen gerade nicht benötigten dafür aus.

- Den virtuellen Speicher kann die CPU dank MMU so ansprechen, als wäre er real existierendes RAM.

Address Unit: Die AU sorgt für die Berechnung der Adresse. In modernen CPUs verseht eine leistungsfähigere MMU diesen Dienst.

Busschnittstelle (BIU)

- Die Busschnittstelle verbindet die internen Busse des Prozessors mit der Außenwelt.

- Sie enthält Puffer zur Zwischenspeicherung von Adressen, Daten und Steuersignalen.

- Die CPU arbeitet intern mit einer möglichst niedrigen Spannung, damit die Erwärmung bei hohen Taktfrequenzen in erträglichen Grenzen bleibt.

- Die BIU sorgt deshalb auch für eine Pegelanpassung zwischen dem CPU-Kern und dem externen Bussystem.

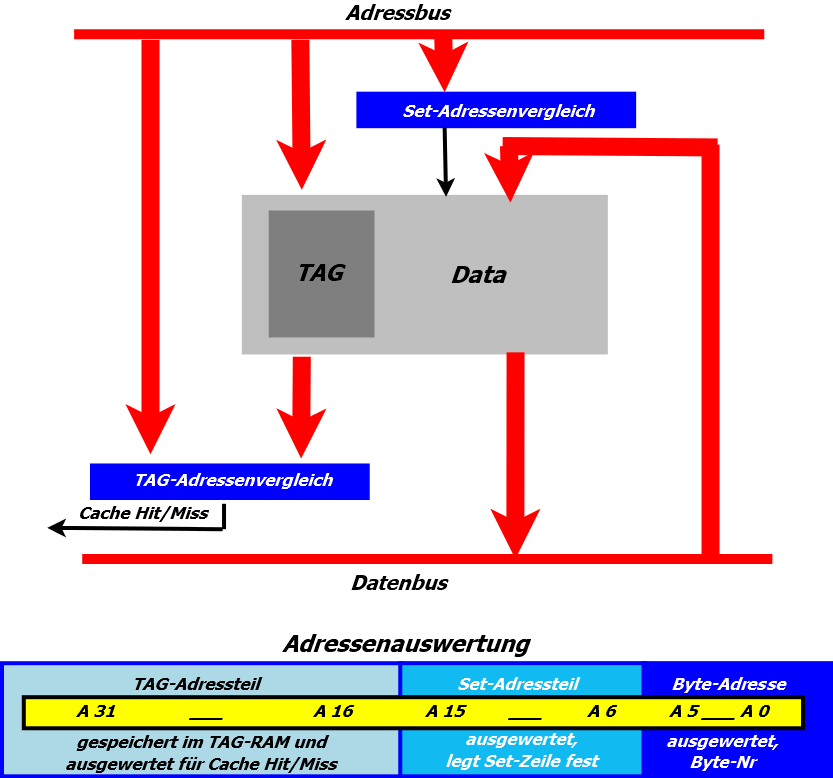

Cache-Grundlagen

- Zur Steigerung der Arbeitsleistung sitzt in der CPU zwischen den extrem schnellen Funktionseinheiten und dem vergleichsweise sehr langsamen Arbeitsspeicher der L1-Cache.

- Aus Platzgründen kann der L1-Cache in der CPU nicht besonders groß sein.

- Er bewegt sich in der Regel in Größenordnungen von 16 bis 64 KByte.

- Die Kunst besteht also darin, den schnellen kleinen Speicher so mit dem langsamen großen Arbeitsspeicher zu kombinieren, dass sich eine möglichst schnelle Gesamtlösung ergibt.

Cache Interna: Der prinzipielle Aufbau eines Caches (oben) sowie die Adressauswertung im Cache-Controller (unten).

- Bild 6 zeigt die Auswertung einer 32-Bit-Adresse nach diesem Prinzip.

Als einfache Analogie betrachten wir einen Briefträger bei der Arbeit:

- Er trägt in einer Stadt (Arbeitsspeicher) die Post (Daten) aus.

- Dafür sortiert er die Post in seiner Tasche nach Straßen (Tag).

- In einer Straße holt er sich die hierfür bestimmte Post heraus und verteilt sie an die Häuser (Set-Zeile).

- Um in Mehrfamilienhäusern auch den richtigen Briefkasten zu erwischen, benötigt er noch den Familiennamen (Byte-Nummer).

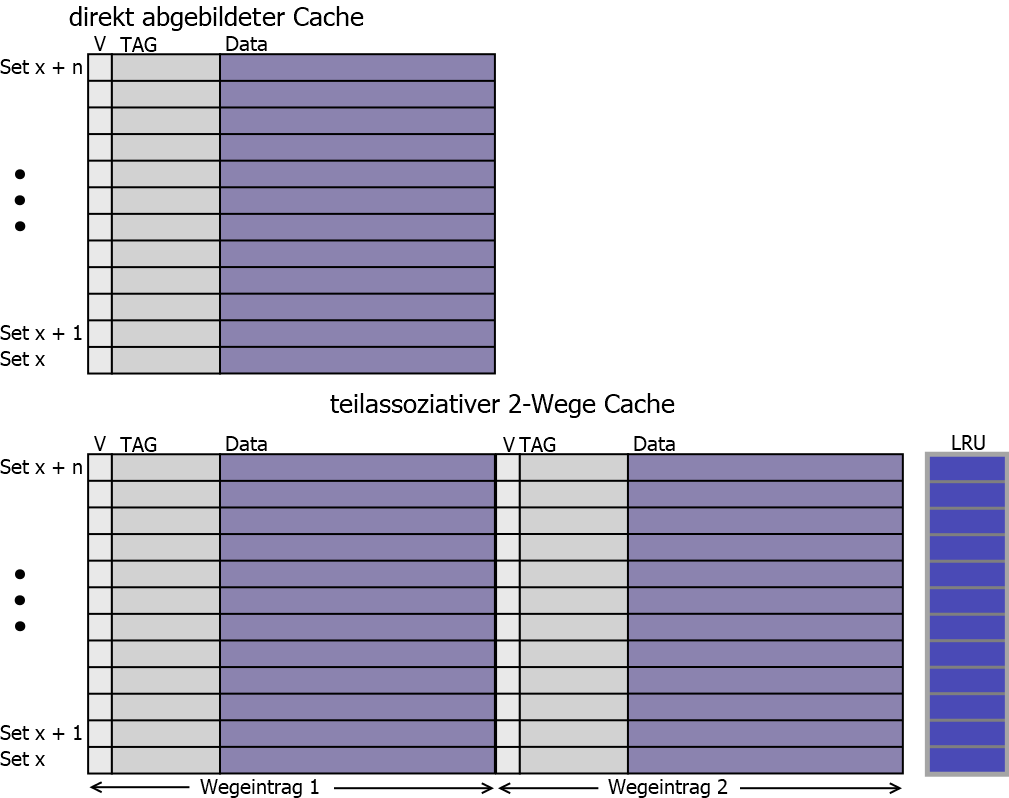

Cache-Organisation

- Der direkt abgebildete (direct mapped) Cache im Bild unten ist die einfachste Form.

- Jedem Set ist nur ein Cache-Eintrag zugeordnet.

- Dadurch deckt man im Arbeitsspeicher einen Block von x+n Sets ab.

Assoziativspeicher: Der teilassoziative Mehrweg-Cache beinhaltet im Prinzip mehrere Direct Mapped Caches plus Statistik-Bits (LRU).

Der Briefträger hat dieses Problem ebenfalls:

- Wenn er einen Abstecher in eine Seitenstraße macht, muss er den nach Straßen vorsortierten Briefstapel zurücklegen und den für die Seitenstraße herausholen.

- Die Lösung des Problems sind teilassoziative Mehrweg-Caches.

- Auch dieser Cache-Typ speichert nur einen Teil der Adresse im Tag ab.

- Taucht ein Tag aber nochmals auf, erfolgt kein Komplettaustausch des Speicherblocks.

- Die Hardware merkt sich den Eintrag wieder in der gleichen Set-Zeile.

- Allerdings erfolgt die Speicherung in einer weiteren Ebene (Weg), sodass die erste Zeile nicht überschrieben werden muss.

- Die Ebenenoder Wegauswahl erfolgt über den Set-Adressteil.

Mit einer Mehrwegsortierung arbeitet auch der Briefträger schneller:

- Er hat sich die Post nicht nur in Straßenzüge (Tag) unterteilt, sondern nochmals mit einem Gummiband hinsichtlich der Straßenseite gebündelt (Set-Weg).

- Bei einem Abstecher in die Seitenstrasse greift er sich nur das Briefbündel für eine Straßenseite.

- Dafür legt er nur eines der zwei Bündel der alten Straße weg - und zwar das von der anderen Straßenseite.

- Wenn er aus der Seitenstrasse zurückkommt, hat er immer noch das Bündel der Seite in der Hand, bei der er abgebogen ist.

- Ein Mehrweg-Cache ist ein vervielfachter Direct Mapped Cache.

- Der Schaltungsaufwand für einen teilassoziativen 2-Wege-Cache ist demnach doppelt so hoch wie bei der einfachen Version.

- Bei einem 4-Wege-Cache vervierfacht er sich.

- Irgendwann sind jedoch auch die Ebenen eines Mehrweg-Caches voll.

- Mittels zusätzlich gespeicherter LRU-Bits kann der Cache dann feststellen, welcher Eintrag in welcher Ebene am längsten nicht mehr benutzt wurde.

- Dieser Wegeintrag wird dann überschrieben.

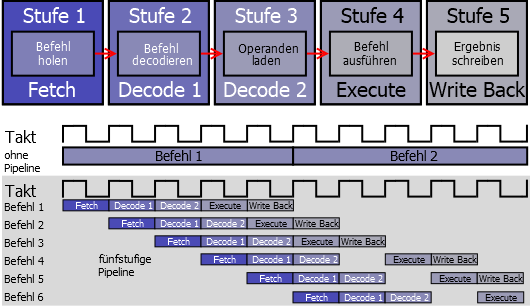

Pipeline-Verfahren

- Bis jetzt sind wir davon ausgegangen, dass die CPU die Befehle nach dem klassischen Von-Neumann-Prinzip nacheinander verarbeitet.

- Jeder Befehl wird innerhalb einer bestimmten Zeit (Taktzyklus) erledigt, dann ist der Nächste dran.

- Wenn man der BIU erlaubt, schon Befehle aus dem Speicher zu holen während die CU gerade einen analysiert, hat man zwei Arbeitsschritte parallelisiert.

- Es sind also zwei Befehle gleichzeitig in Teilbearbeitung. Überträgt man das Prinzip auf alle beteiligten Funktionseinheiten, erhöht sich die Zahl der Teilbearbeitungen weiter.

- Dieses Pipeline-Prinzip verarbeitet aber die eingehenden Befehle und Daten immer noch Schritt für Schritt.

Pipeline in Funktion: Mit der Pipelining-Technik lässt sich die Befehlsausführung beschleunigen.

Superskalare Architektur

- Wenn schon eine Pipeline die Geschwindigkeit erhöht, geht es mit Zweien noch schneller.

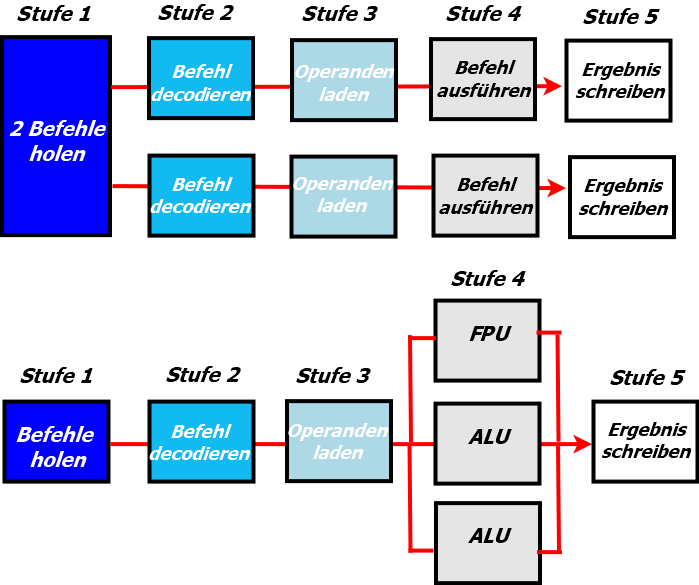

- In Bild 9 "Parallel ist schneller" ist im oberen Teil ein solcher Ansatz zu sehen.

- Auf diese Weise arbeitet beispielsweise der Intel Pentium.

- Um unnötige Probleme mit Abhängigkeiten zwischen den Befehlen zu minimieren, arbeitet die Intel-CPU allerdings nur bei Kommandos gleichzeitig mit beiden Pipelines, die gut zueinander passen.

Parallel ist schneller: Superskalare Architekturen mit einer doppelten Pipeline (oben) und parallel arbeitenden Ausführungseinheiten

(unten).

Sprungvorhersage

Die Sprungvorhersage (englisch branch prediction) wird in der (Mikro-)Rechnerarchitektur verwendet und behandelt das Problem von Mikroprozessoren, alle Stufen ihrer Pipeline möglichst immer und sinnvoll auszulasten.

Inhaltsverzeichnis:

1. Übersicht

2. Funktionsweise: Statische Sprungvorhersage & Dynamische Sprungvorhersage

3. Dynamische Sprungvorhersagetechniken: Branch History Table (BHT),n-Bit träger Automat,1-Bit-Automat & gshare

4. Statische Sprungvorhersagetechnike: Stall/Freeze, Predict taken, Predict not taken & Delayed Branches

5. Sprungzielvorhersage-Techniken: Branch Target Buffer (BTB) & Call-Return-Stapel

1. Übersicht:

Unter Sprungvorhersage (auch Verzweigungsvorhersage) versteht man:

- Die Vorhersage, ob ein bedingter Sprung ausgeführt wird

- Die Zieladresse eines Sprunges zu ermitteln

Zwei Arten von Sprüngen:

- Bedingter Sprung: Jcondition Adresse

- Unbedingter Sprung: JMP Adresse, JMP BerechneteAdresse, CALL Adresse, CALL BerechneteAdresse, RET

In modernen Prozessoren werden Maschinenbefehle in mehreren Verarbeitungsschritten innerhalb einer Verarbeitungskette (Pipeline) ausgeführt. Um die Leistungsfähigkeit des Prozessors zu maximieren, wird, nachdem ein Befehl in die Pipeline geladen wurde und z. B. im nächsten Schritt mit der Analyse des Befehls fortgefahren werden soll, gleichzeitig mit dem Laden des nächsten Befehles begonnen. Es befinden sich also (meistens) eine ganze Reihe von Befehlen zur sequentiellen Abarbeitung in der Pipeline. Wird jetzt am Ende der Pipeline festgestellt, dass ein bedingter Sprung ausgeführt wird, so sind alle in der Pipeline anstehenden und teilabgearbeiteten Befehle ungültig. Der Prozessor löscht jetzt die Pipeline und lädt diese dann von der neuen Programmcodeadresse neu. Je mehr Stufen die Pipeline hat, desto mehr schon berechnete Zwischenergebnisse müssen verworfen werden und umso mehr Takte wird die Pipeline nur partiell genutzt. Das reduziert die Abarbeitungsgeschwindigkeit von Programmen und reduziert die Energieeffizienz.

Das Ziel ist möglichst frühes Erkennen eines Sprungbefehls und Erkennen seiner Sprungzieladresse, damit gleich die Daten der Zieladresse dem Sprungbefehl in die Pipeline folgen können.

2. Funktionsweise:

- Statische Sprungvorhersage: Die statische Sprungvorhersage ändert ihre Vorhersage während des Programmablaufs nicht. Sie erreicht dadurch nur eine Vorhersagegenauigkeit von 55 bis 80 %. Diese Technik geht von bekannten Tatsachen aus, z. B. dass Schleifen häufig Sprünge ausführen, während dies bei Auswahlverfahren seltener vorkommt. Manche Compiler unterstützen den Mechanismus auch mit speziellen Flags im Befehlscode (Vorhersage wird beim Kompilieren eingebaut).

- Dynamische Sprungvorhersage: Die dynamische Sprungvorhersage geschieht zur Laufzeit durch eine elektronische Verschaltung innerhalb der CPU. Sie benutzt verschiedene Techniken zur Erzeugung einer Vorhersage. Ihre Vorhersagegenauigkeit liegt bei bis zu 98 %. Die einfachste Methode spekuliert anhand der Sprungrichtung: Sprünge im Programmcode zurück sind in der Regel Schleifen, die oft mehrfach durchlaufen werden, sodass bei dieser prophylaktisch die Pipeline mit dem zurückliegenden Code gefüllt wird.Erkannte bedingungslose Sprünge werden einfach vorab aus der Befehlswarteschlange aussortiert und diese dann mit dem Code vom Sprungziel weitergefüllt, bevor diese in die Pipeline eintreten.(„Branch folding“)

3. Dynamische Sprungvorhersagetechniken:

- Branch History Table (BHT): Die BHT (auch Branch-Prediction Buffer) versucht, wie ihr Name schon sagt, ebenfalls die letzten Sprünge mitzuprotokollieren. Dazu verwendet sie einen Teil der Sprungbefehlsadresse als Hashwert. Im Allgemeinen nimmt man dafür den niederwertigen Adressanteil. Diese Adressteile können natürlich nicht immer eindeutig sein, so dass es Kollisionen geben kann (mehrere unterschiedliche Sprünge belegen denselben Platz in der Tabelle).Die Tabelle wird nach jedem Sprung aktualisiert.

- 1-Bit-Automat: Wird ein gespeicherter Sprung genommen, wird dessen Bit von 0 auf 1 gesetzt. Ein Problem ist aber, dass er alternierende Sprünge nicht berücksichtigt (bei Sprüngen, die z. B. nur bei jedem 2. Schleifendurchlauf stattfinden, würde das Bit immer wieder invertiert werden). Die Lösung hierfür ist ein n-Bit-Automat.

- n-Bit träger Automat: Dieser setzt das Korrektheitsbit erst nach den n Fehlschlägen auf 0. Im Allgemeinen wird n = 2 verwendet. (Tests haben gezeigt, dass ab n > 2 die Leistungssteigerung nur noch minimal ist.) Beim ersten Schleifendurchlauf ist der Zustand 00, und die Bedingung sei wahr. Damit geht der Zustand nach 01 über. Ist beim nächsten Schleifendurchlauf die Bedingung wieder wahr, wird der Zustand 10 und sagt daher auch für alle weiteren Sprünge eine wahre Sprungbedingung vorher. Ist beim zweiten Durchlauf die Bedingung falsch, so geht der Zustand wieder nach 00 zurück. Ist der Zustand 11, so muss die Sprungbedingung zweimal falsch gewesen sein, bevor die Vorhersage wieder „falsch“ lautet. Mit anderen Worten: Nachdem zweimal in die gleiche Richtung gesprungen wurde, wird diese Richtung nun auch für die weiteren Sprünge vorhergesagt. Es lässt sich errechnen, dass bei diesem Verfahren die Wahrscheinlichkeit für die richtige Vorhersage bei 83 % liegt.

- gshare: Bei gshare werden der Adressteil und die Global History mit XOR verknüpft und in eine Tabelle abgelegt. Die Informationen der Tabelle werden dann zur Sprungvorhersage herangezogen. gshare kombiniert somit Per-Address History mit Global History. Da hier XOR als Hashverfahren genommen wird, können wieder Kollisionen entstehen. Das Verfahren findet z. B. im AMD Athlon und Pentium III Anwendung.

4. Statische Sprungvorhersagetechniken:

- Stall/Freeze: Diese Technik hält einfach die ganze Pipeline kurz an. Wird in der ID-Stage (Instruction Decoding) ein Sprungbefehl festgestellt, wird die Pipeline solange angehalten (stalled/frozen), bis man in der EX-Stage (Execution) weiß, ob der Sprung ausgeführt wird.

- Sprung wird nicht ausgeführt, macht normal weiter.

- Sprung wird ausgeführt: Setze Programmzähler auf Sprungzieladresse und fülle die Pipeline mit den Instruktionen, die sich am Sprungziel befinden.

- Predict taken: Geht einfach davon aus, dass jeder bedingte Sprung auch ausgeführt wird, d. h., wird in der ID-Stage festgestellt, dass ein Sprungbefehl vorliegt, beginnt die CPU schon mal die Zieladresse zu bestimmen und die dortigen Daten gleich in die Pipeline als Folgeinstruktionen zu laden. Wird in der EX-Stage allerdings festgestellt, dass der Sprung doch nicht stattfindet, war die vorherige Arbeit umsonst (verwendet bei Schleifen).

- Predict not taken: Geht davon aus, dass jeder bedingte Sprung nicht ausgeführt wird und macht normal weiter. Dies bedeutet (sollte der Sprung wirklich nicht ausgeführt werden) einen guten Performancegewinn. Sollte in der EX-Stage festgestellt werden, dass der Sprung wider Erwarten doch ausgeführt wird, muss die Folgeinstruktion angehalten, der PC auf die Sprungzieladresse gestellt und damit dann die Pipeline gefüllt werden (verwendet bei Auswahlverfahren).

- Delayed Branches: Delayed Branches stellen keine Sprung-Vorhersage dar. Sprungbefehle werden 1 bis 3 Befehle im Befehlsstrom nach vorn gezogen kodiert, die folgenden 1 bis 3 Befehle werden unabhängig vom Sprungbefehl immer ausgeführt.

5. Sprungzielvorhersage-Techniken:

Besser als eine bloße Sprungvorhersage ist gleich eine Sprungzielvorhersage. Sobald man in der ID-Stage erkennt, dass es sich um einen Sprung handelt, kann man prüfen, ob dieser Sprung schon mal stattfand und ggf. sein Sprungziel aus einem Puffer holen. Somit kann man den Programmzähler sofort auf dieses Sprungziel stellen und die dortigen Instruktionen in die Pipeline laden.

- Branch Target Buffer (BTB): Der BTB (auch Sprungzielpuffer oder Branch Target Address Cache, BTAC): Dient der Vorhersage der Folgeadresse, noch bevor der Befehl dekodiert wurde, d. h. bevor feststeht, ob es sich überhaupt um einen Sprungbefehl handelt. Auf diesem Wege wird die andernfalls unvermeidliche Pipelinelücke vermieden und somit die Verzweigungskosten gesenkt. Die Vorhersage wird anhand in einer Tabelle gespeicherter (vorher tatsächlich ausgeführter) Sprünge getroffen.

Diese Tabelle enthält:

- Vorhersageinformationen

- Zieladressen

- Tags

Der BTB liefert immer eine Adresse zurück. Wird ein unbekannter Sprung abgefragt, so liefert er einfach die Folgeadresse. Wird aber ein bekannter Sprung abgefragt, so liefert er die Zieladresse.Der BTB kann nicht immer korrekt arbeiten. Da z. B. RETURN-Anweisungen variable Zieladressen haben (Moving Targets), kann der BTB zu einem korrekten Sprung eine falsche Zieladresse abspeichern. Da in modernen Programmierhochsprachen objektorientiert programmiert wird, kommt es zu häufigen Methodenaufrufen und somit zu vielen Moving Targets. Um diese in der Hinsicht fatale Schwäche zu beheben, werden BTBs um einen Call-Return-Stapel erweitert.

- Call-Return-Stapel: Dieser Stapel speichert alle Return-Adressen nach dem LIFO-Prinzip. Weiterhin wird von speziellen Call- und Return-Befehlen im Befehlssatz ausgegangen (wird also von einem normalen Sprung unterschieden).

Sonderbehandlung beider Sprünge im Branch Target Buffer (BTB):

- Call: Beim Aufruf wird die Return-Adresse auf dem Call-Return-Stack abgelegt.

- Return: RET-Befehle sind im BTB speziell markiert. Beim Fetchen eines Befehls von einer so markierten Adresse wird statt der Zieladresse aus dem BTB die oberste Adresse des Call-Return-Stacks verwendet.